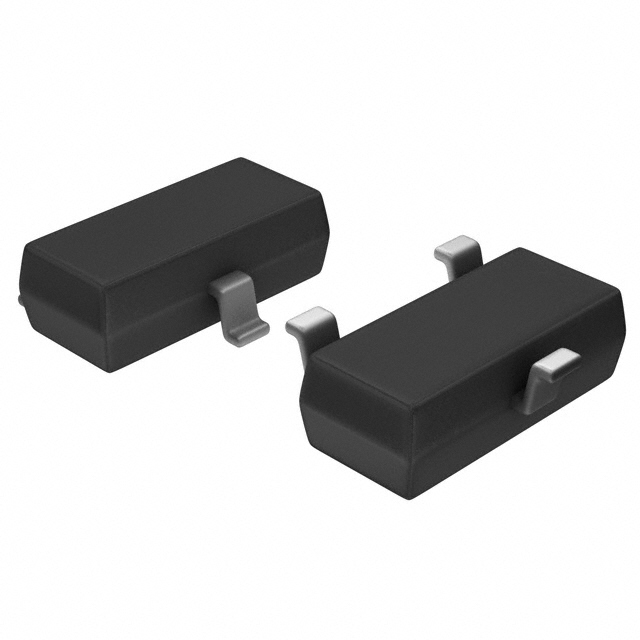

NXP LPC1758FBD80Y

ARM® Cortex®-M3100 МГц512 КБ (512К x 8)

Сравнить

₽600.64

Обновление цены:2025-03-14Гарантия качества Bostock

Overview

■ ARM Cortex-M3 processor, running at frequencies of up to 100 MHz (LPC1758/56/57/54/52/51) or of up to 120 MHz (LPC1759). A Memory Protection Unit (MPU) supporting eight regions is included. ■ ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC). ■ Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator enables high-speed 120 MHz operation with zero wait states. ■ In-System Programming (ISP) and In-Application Programming (IAP) via on-chip bootloader software. ■ On-chip SRAM includes: ♦ Up to 32 kB of SRAM on the CPU with local code/data bus for high-performance CPU access. ♦ Two/one 16 kB SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for Ethernet (LPC1758 only), USB, and DMA memory, as well as for general purpose CPU instruction and data storage. ■ Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with the SSP, I2S-bus, UART, the Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, and for memory-to-memory transfers. ■ Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC (LPC1758 only), and the USB interface. This interconnect provides communication with no arbitration delays. ■ Split APB bus allows high throughput with few stalls between the CPU and DMA. ■ Serial interfaces: ♦ On the LPC1758 only, Ethernet MAC with RMII interface and dedicated DMA controller. ♦ USB 2.0 full-speed device/Host/OTG controller with dedicated DMA controller and on-chip PHY for device, Host, and OTG functions. The LPC1752/51 include a USB device controller only. ♦ Four UARTs with fractional baud rate generation, internal FIFO, and DMA support. One UART has modem control I/O and RS-485/EIA-485 support, and one UART has IrDA support. ♦ CAN 2.0B controller with two (LPC1759/58/56) or one (LPC1754/52/51) channels. ♦ SPI controller with synchronous, serial, full duplex communication and programmable data length. ♦ Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces can be used with the GPDMA controller. ♦ Two I2C-bus interfaces supporting fast mode with a data rate of 400 kbit/s with multiple address recognition and monitor mode. ♦ On the LPC1759/58/56 only, I2S (Inter-IC Sound) interface for digital audio input or output, with fractional rate control. The I2S-bus interface can be used with the GPDMA. The I2S-bus interface supports 3-wire and 4-wire data transmit and receive as well as master clock input/output. ■ Other peripherals: ♦ 52 General Purpose I/O (GPIO) pins with configurable pull-up/down resistors. All GPIOs support a new, configurable open-drain operating mode. The GPIO block is accessed through the AHB multilayer bus for fast access and located in memory such that it supports Cortex-M3 bit banding and use by the General Purpose DMA Controller. ♦ 12-bit Analog-to-Digital Converter (ADC) with input multiplexing among six pins, conversion rates up to 200 kHz, and multiple result registers. The 12-bit ADC can be used with the GPDMA controller. ♦ On the LPC1759/58/56/54 only, 10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA support. ♦ Four general purpose timers/counters, with a total of three capture inputs and ten compare outputs. Each timer block has an external count input. Specific timer events can be selected to generate DMA requests. ♦ One motor control PWM with support for three-phase motor control. ♦ Quadrature encoder interface that can monitor one external quadrature encoder. ♦ One standard PWM/timer block with external count input. ♦ Real-Time Clock (RTC) with a separate power domain and dedicated RTC oscillator. The RTC block includes 20 bytes of battery-powered backup registers. ♦ Watchdog Timer (WDT). The WDT can be clocked from the internal RC oscillator, the RTC oscillator, or the APB clock. ♦ ARM Cortex-M3 system tick timer, including an external clock input option. ♦ Repetitive Interrupt Timer (RIT) provides programmable and repeating timed interrupts. ♦ Each peripheral has its own clock divider for further power savings. ■ Standard JTAG test/debug interface for compatibility with existing tools. Serial Wire Debug and Serial Wire Trace Port options. ■ Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution. ■ Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes. ■ Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down. ■ Single 3.3 V power supply (2.4 V to 3.6 V). ■ One external interrupt input configurable as edge/level sensitive. All pins on Port 0 and Port 2 can be used as edge sensitive interrupt sources. ■ Non-maskable Interrupt (NMI) input. ■ The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in Deep sleep, Power-down, and Deep power-down modes. ■ Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet wake-up interrupt (LPC1758 only), CAN bus activity, Port 0/2 pin interrupt, and NMI). ■ Brownout detect with separate threshold for interrupt and forced reset. ■ Power-On Reset (POR). ■ Crystal oscillator with an operating range of 1 MHz to 25 MHz. ■ 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock. ■ PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator. ■ USB PLL for added flexibility. ■ Code Read Protection (CRP) with different security levels. ■ Unique device serial number for identification purposes. ■ Available as 80-pin LQFP package (12 mm × 12 mm × 1.4 mm).

Features

LPC17xx SeriesARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

Split APB bus allows high throughput with few stalls between the CPU and DMA

In-System Programming (ISP) and In-Application Programming (IAP) via on-chip bootloader software.

Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator enables high-speed 120 MHz operation with zero wait states.

ARM Cortex-M3 processor, running at frequencies of up to 100 MHz (LPC1758/56/57/54/52/51) or of up to 120 MHz (LPC1759). A Memory Protection Unit (MPU) supporting eight regions is included.

On-chip SRAM includes:

Up to 32 kB of SRAM on the CPU with local code/data bus for high-performance CPU access.

Two/one 16 kB SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for Ethernet (LPC1758 only), USB, and DMA memory, as well as for general purpose CPU instruction and data storage.

Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with the SSP, I2S-bus, UART, the Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, and for memory-to-memory transfers.

Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC (LPC1758 only), and the USB interface. This interconnect provides communication with no arbitration delays.

Applications

Automotive

Personal electronics

Communications equipment

- Стоимость фрахта начинается с $40, но цены в некоторых странах, таких как ЮжнаяАфрика, Бразилия, Индия, Пакистан и Израиль, могут отличаться.

- Основные расходы на перевозку посылок весом 0,5 кг или эквивалентного объема зависят от часовых поясов и страны.

- В настоящее время наша продукция поставляется с использованием DHL, SF и UPS. Для меньшего числа авиакомпаний FedEx является предпочтительным вариантом.

- После отгрузки предполагаемое время доставки зависит от выбранного метода перевозки.

Подготовить продукт

вакуумная упаковка

антистатический пакет

индивидуальная упаковка

упаковочная коробка

штрихкод этикетка для доставки

NXP USA Inc.

NXP USA Inc. является американским филиалом компании NXP Semiconductors, которая занимается проектированием, разработкой, производством и продажей полупроводниковой продукции. Компания специализируется на производстве полупроводниковых пластин в Остине (штат Техас) и Чандлере (штат Аризона) и выпускает высокопроизводительные решения для автомобильного, промышленного и коммуникационного рынков.

Популярные номера деталей

MIMX8QM5AVUFFAB

MPU I.MX8 QUAD MAX

₽672.22В наличии :заказ по расписаниюMK22FN512VDC12

IC MCU 32BIT 512KB FLSH 121XFBGA

₽818.41В наличии :17229MIMX8MM6CVTKZAA

IC MPU I.MX8MM 1.6GHZ 486LFBGA

₽2401.61В наличии :заказ по расписаниюMRFE6VS25GNR1

RF MOSFET LDMOS 50V TO270-2 GULL

₽1170.96В наличии :887LPC54616J512ET100E

IC MCU 32BIT 512KB FLSH 100TFBGA

₽3689.62В наличии :заказ по расписанию

MKL03Z32VFK4R

IC MCU 32BIT 32KB FLASH 24QFN

₽206.88В наличии :14033FS32K144UAT0VLLT

IC MCU 32BIT 512KB FLASH 100LQFP

₽176.73В наличии :10566MK20DX256VMC10

IC MCU 32B 256KB FLASH 121MAPBGA

₽741.47В наличии :4304MC9S08PA8AVTJ

IC MCU 8BIT 8KB FLASH 20TSSOP

₽183.62В наличии :заказ по расписаниюCBTL02042ABQ,115

IC MUX/DEMUX 2:1 PCI 20DHVQFN

₽111.86В наличии :заказ по расписанию

MC9S12XEP100MAG

IC MCU 16BIT 1MB FLASH 144LQFP

₽689.59В наличии :22103MK64FX512VLL12

IC MCU 32BIT 512KB FLASH 100LQFP

₽1212.46В наличии :5MKL17Z256VFT4R

IC MCU 32BIT 256KB FLASH 48QFN

₽4039.60В наличии :заказ по расписаниюMIMX8MQ6DVAJZAB

IC MPU I.MX8MQ 1.5GHZ 621FCPBGA

₽2654.59В наличии :заказ по расписаниюMIMXRT1064DVL6B

IC MCU 32BIT 4MB FLASH 196MAPBGA

₽720.48В наличии :заказ по расписанию

MIMX8QM5AVUFFAB

MPU I.MX8 QUAD MAX

₽672.22В наличии :заказ по расписаниюMK22FN512VDC12

IC MCU 32BIT 512KB FLSH 121XFBGA

₽818.41В наличии :17229MIMX8MM6CVTKZAA

IC MPU I.MX8MM 1.6GHZ 486LFBGA

₽2401.61В наличии :заказ по расписаниюMRFE6VS25GNR1

RF MOSFET LDMOS 50V TO270-2 GULL

₽1170.96В наличии :887LPC54616J512ET100E

IC MCU 32BIT 512KB FLSH 100TFBGA

₽3689.62В наличии :заказ по расписанию

MKL03Z32VFK4R

IC MCU 32BIT 32KB FLASH 24QFN

₽206.88В наличии :14033FS32K144UAT0VLLT

IC MCU 32BIT 512KB FLASH 100LQFP

₽176.73В наличии :10566MK20DX256VMC10

IC MCU 32B 256KB FLASH 121MAPBGA

₽741.47В наличии :4304MC9S08PA8AVTJ

IC MCU 8BIT 8KB FLASH 20TSSOP

₽183.62В наличии :заказ по расписаниюCBTL02042ABQ,115

IC MUX/DEMUX 2:1 PCI 20DHVQFN

₽111.86В наличии :заказ по расписанию

MC9S12XEP100MAG

IC MCU 16BIT 1MB FLASH 144LQFP

₽689.59В наличии :22103MK64FX512VLL12

IC MCU 32BIT 512KB FLASH 100LQFP

₽1212.46В наличии :5MKL17Z256VFT4R

IC MCU 32BIT 256KB FLASH 48QFN

₽4039.60В наличии :заказ по расписаниюMIMX8MQ6DVAJZAB

IC MPU I.MX8MQ 1.5GHZ 621FCPBGA

₽2654.59В наличии :заказ по расписаниюMIMXRT1064DVL6B

IC MCU 32BIT 4MB FLASH 196MAPBGA

₽720.48В наличии :заказ по расписанию

MIMX8QM5AVUFFAB

MPU I.MX8 QUAD MAX

₽672.22В наличии :заказ по расписаниюMK22FN512VDC12

IC MCU 32BIT 512KB FLSH 121XFBGA

₽818.41В наличии :17229MIMX8MM6CVTKZAA

IC MPU I.MX8MM 1.6GHZ 486LFBGA

₽2401.61В наличии :заказ по расписаниюMRFE6VS25GNR1

RF MOSFET LDMOS 50V TO270-2 GULL

₽1170.96В наличии :887LPC54616J512ET100E

IC MCU 32BIT 512KB FLSH 100TFBGA

₽3689.62В наличии :заказ по расписанию

Новosti в реальном времени

Bostock по цифрам

Доход: 85M

$85 миллионов в доходах в 2022 году, увеличение на 63% по сравнению с 2021 годом.

Страны: 105

Bostock обслуживает клиентов в 105 странах мира.

Отгруженные части: 25M+

Мы отгрузили более 25 миллионов частей за последние пять лет, что составляет увеличение на 148% по сравнению с предыдущими пятью годами.

Производители: 950

В 2022 году Bostock продал части от более чем 950 производителей.

Популярные продукты

MC9S08PA8AVTJ

NXP USA Inc.

IC MCU 8BIT 8KB FLASH 20TSSOP

MIMXRT1064DVL6B

NXP USA Inc.

IC MCU 32BIT 4MB FLASH 196MAPBGA

MKL17Z256VFT4R

NXP USA Inc.

IC MCU 32BIT 256KB FLASH 48QFN

MK20DX256VMC10

NXP USA Inc.

IC MCU 32B 256KB FLASH 121MAPBGA

MK22FN512VDC12

NXP USA Inc.

IC MCU 32BIT 512KB FLSH 121XFBGA

MC9S12XEP100MAG

NXP USA Inc.

IC MCU 16BIT 1MB FLASH 144LQFP

LPC54616J512ET100E

NXP USA Inc.

IC MCU 32BIT 512KB FLSH 100TFBGA

MKL03Z32VFK4R

NXP USA Inc.

IC MCU 32BIT 32KB FLASH 24QFN

FS32K144UAT0VLLT

NXP USA Inc.

IC MCU 32BIT 512KB FLASH 100LQFP

MK64FX512VLL12

NXP USA Inc.

IC MCU 32BIT 512KB FLASH 100LQFP